- Using USB Blaster / USB Blaster II under Linux

- Driver Setup for recent udev

- Driver Setup for Ubuntu

- Первый проект на FPGA Altera и подключение USB-Blaster в Linux

- Using Altera’s Intel’s USB-Blaster on Debian Linux

- Allowing non-root access to the USB-Blaster device

- Mounting the usbfs filesystem

- Configuring jtagd

- Testing your setup

- Programming your FPGA device

Using USB Blaster / USB Blaster II under Linux

Quartus® II software does not need any specific usb drivers on Linux to access the USB-BlasterTM and USB-Blaster II download cable. By default, root is the only user allowed to use these devices.You must change the permissions on the device files before you can use the USB-Blaster or USB-Blaster IIdownload cable to program devices with Quartus II software.

You must have system administration (root) privileges to add udev rules to correctly configure the access rights.

Driver Setup for recent udev

Add a new file /etc/udev/rules.d/92-usbblaster.rules file. Note that the 92 is important for e.g. Debian Wheezy as there is a default rule for «usbfs-like» devices /lib/udev/rules.d/91-permissions.rules specifying a MODE of 664. Because udev assigns priority to rules by the sort order of the file names theyappear in the USB Blaster rules have to be placed in an appropriate file.

# USB-Blaster SUBSYSTEM=="usb", ATTRS=="09fb", ATTRS=="6001", MODE="0666" SUBSYSTEM=="usb", ATTRS=="09fb", ATTRS=="6002", MODE="0666" SUBSYSTEM=="usb", ATTRS=="09fb", ATTRS=="6003", MODE="0666" # USB-Blaster II SUBSYSTEM=="usb", ATTRS=="09fb", ATTRS=="6010", MODE="0666" SUBSYSTEM=="usb", ATTRS=="09fb", ATTRS=="6810", MODE="0666"

Driver Setup for Ubuntu

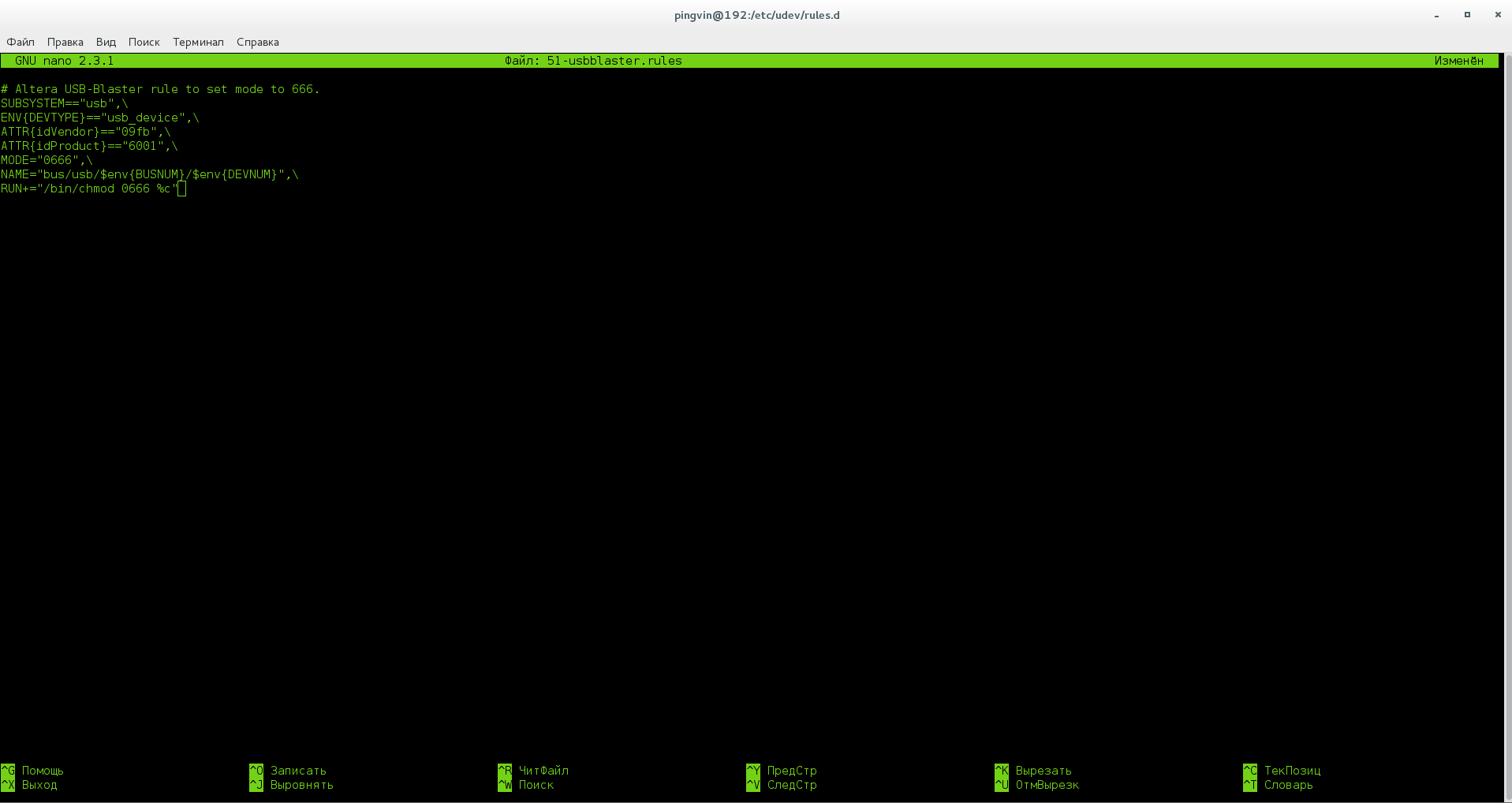

For Ubuntu 12.04/14.04/16.04 create the file /etc/udev/rules.d/51-usbblaster.rules with the following contents:

# USB Blaster SUBSYSTEM=="usb", ENV=="usb_device", ATTR=="09fb", ATTR=="6001", MODE="0666", NAME="bus/usb/$env/$env", RUN+="/bin/chmod 0666 %c" SUBSYSTEM=="usb", ENV=="usb_device", ATTR=="09fb", ATTR=="6002", MODE="0666", NAME="bus/usb/$env/$env", RUN+="/bin/chmod 0666 %c" SUBSYSTEM=="usb", ENV=="usb_device", ATTR=="09fb", ATTR=="6003", MODE="0666", NAME="bus/usb/$env/$env", RUN+="/bin/chmod 0666 %c" # USB Blaster II SUBSYSTEM=="usb", ENV=="usb_device", ATTR=="09fb", ATTR=="6010", MODE="0666", NAME="bus/usb/$env/$env", RUN+="/bin/chmod 0666 %c" SUBSYSTEM=="usb", ENV=="usb_device", ATTR=="09fb", ATTR=="6810", MODE="0666", NAME="bus/usb/$env/$env", RUN+="/bin/chmod 0666 %c"

then insert, or reinsert the USB cable.

Первый проект на FPGA Altera и подключение USB-Blaster в Linux

Продолжаем осваивать FPGA Altera. В первой части я описал процесс установки программного обеспечения Altera Quartus под CentOS7. Теперь уже наконец попробуем что-то сделать «железное», например светодиодики позажигаем. Но прежде небольшое вступление.

Одним из направлений моей деятельности является преподавание в кружке робототехники в небольшом городке Беларуси. Окунувшись во всю эту кухню и поучаствовав в разных конкурсах не только как тренер команды, но и как судья, я пришел к выводу, что ардуино в частности и микроконтроллеры в целом не самая лучшая база для конкурсных роботов (про лего вообще молчу). Многие задачи эффективней решать на уровне голой электроники. Кроме того 90% процентов кружков и «школ» робототехники не дают даже базовых знаний именно электроники, сосредоточившись чисто на «обучении» программированию готовых конструкций. Но чисто электронные роботы (например незаслуженно забытые BEAM) заточены под конкретную задачу и изменение условий конкурса приведет к необходимости существенной перестройки робота, что не всегда возможно. Вот тут я и вспомнил про программируемую логику. В результате поиска информации о применении ПЛИС в обучении я наткнулся на блог Юрия Панчула YuriPanchul. Пользуясь случаем я хочу публично выразить ему свою благодарность. Благодаря ему наш кружок совершенно бесплатно получил плату TerasIC DE0-CV c Altera Cyclone V на борту.

Собственно эта и последующие публикации будут представлять собой реальный учебный материал, который мы реализовываем на кружке. И я буду благодарен за конструктивную критику и замечания, так как применение ПЛИС на кружках для школьников — нехоженая пока область.

Итак, начинаем. В этой публикации будут описаны первые шаги в Quartus, описание элементарной цифровой логики на языке Verilog и загрузка конфигурации в FPGA Altera Cyclone V. Работать мы будем с платой TerasIC DE0-CV, которая имеет на борту встроенный USB-Blaster. Так же затронем и вопрос «запуска» USB-Blaster под Linux.

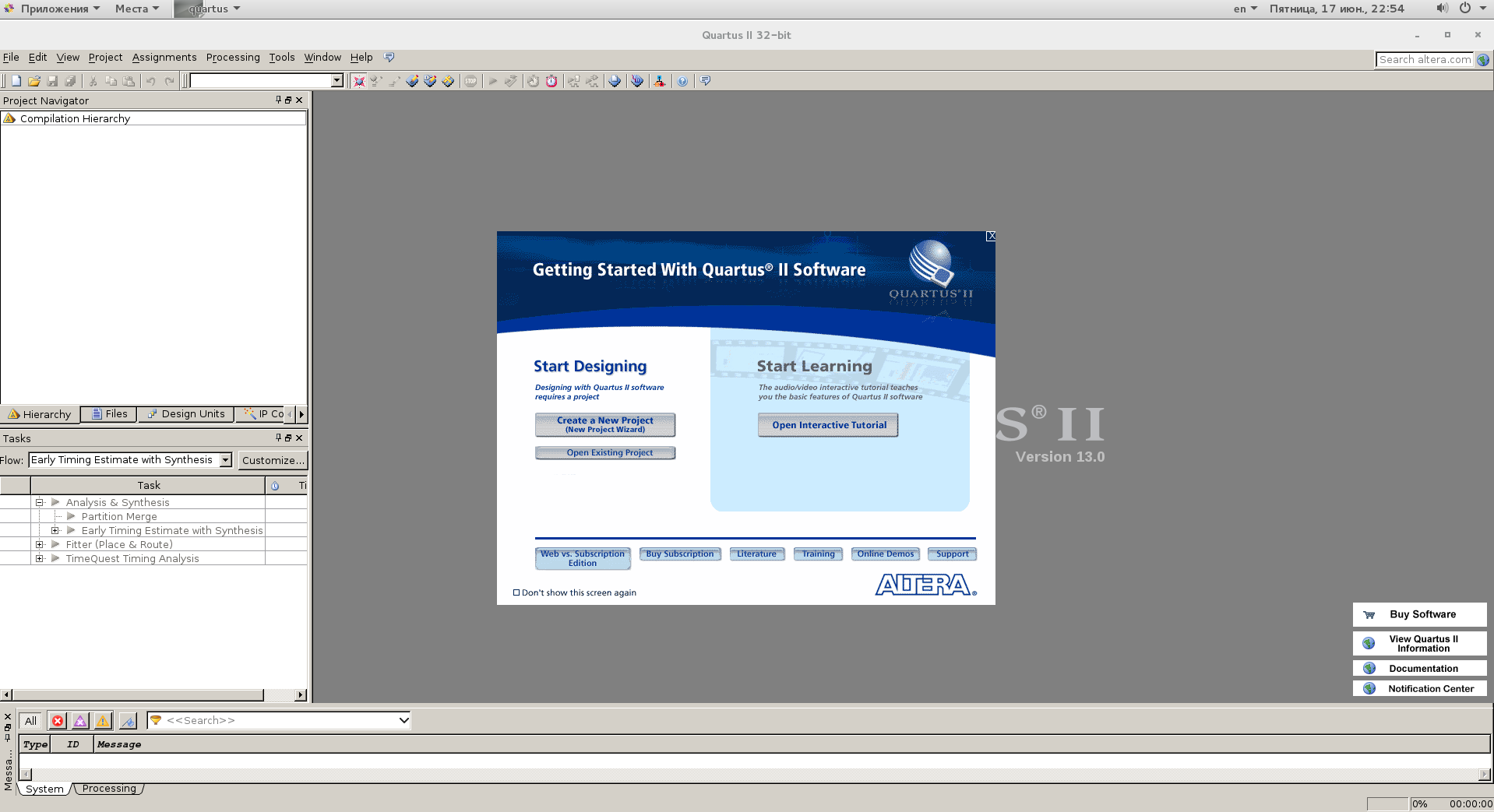

Запускаем Quartus:

Выбираем «Create a New Project». Запускается диалог мастера создания проекта. Тут просто нажимаем Next.

А теперь нам надо выбрать рабочую директорию для проекта (не забываем про права доступа!). Придумываем название проекта:

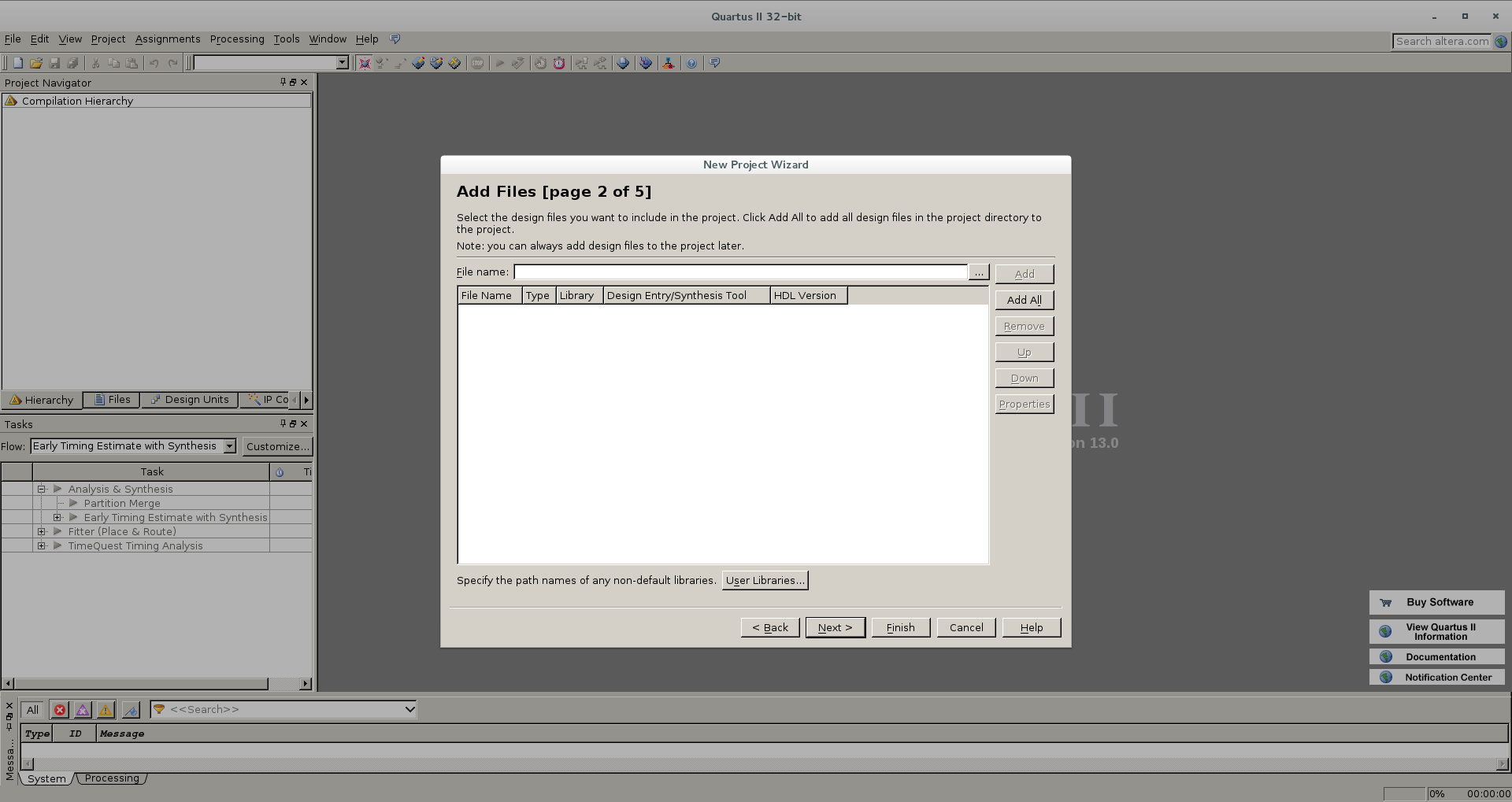

На следующем шаге нам предлагают добавить в проект дополнительные файлы. На данном этапе нам это не нужно, но в будущем для облегчения работы стоит добавлять как минимум файл назначения выводов.

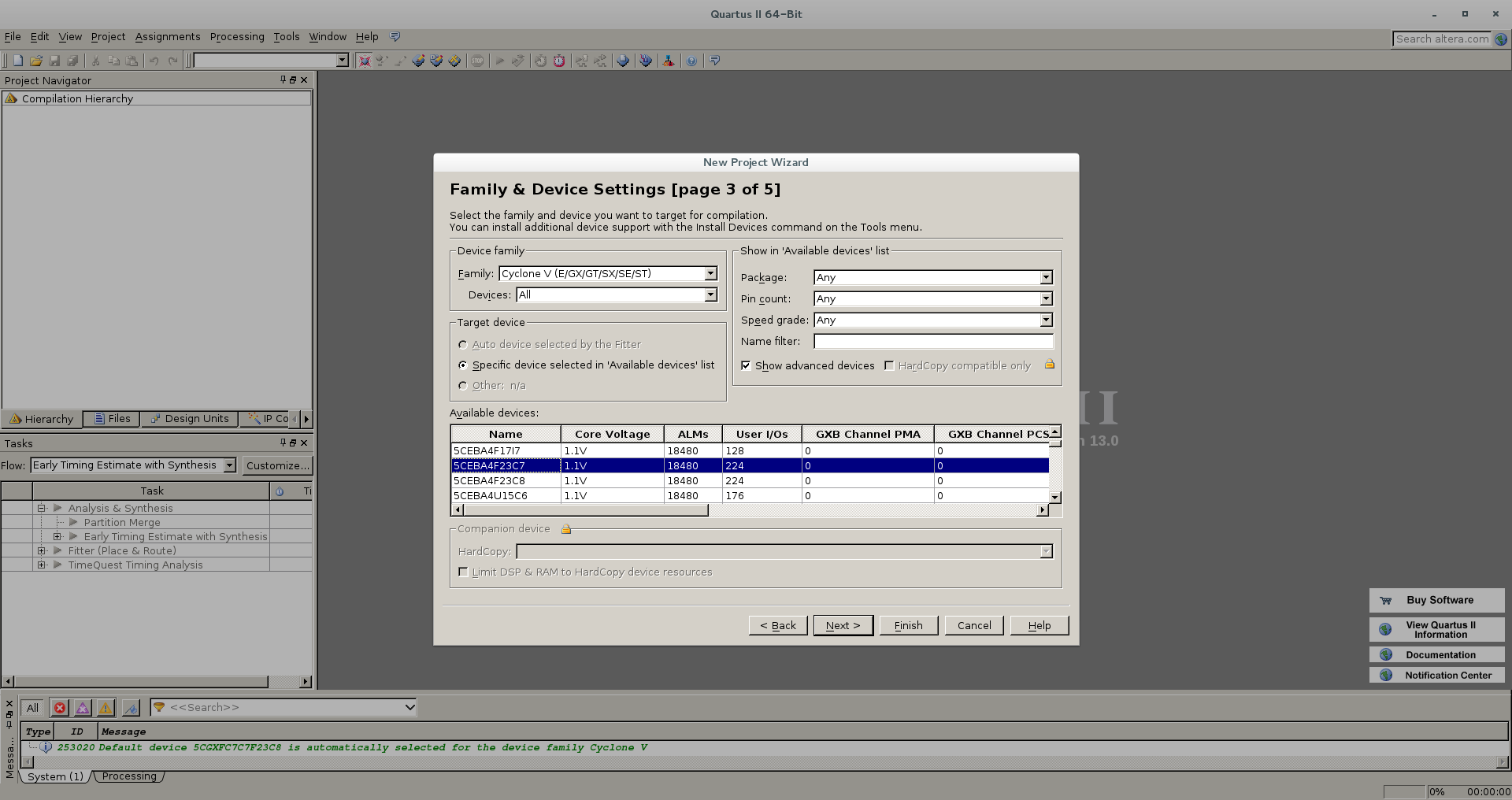

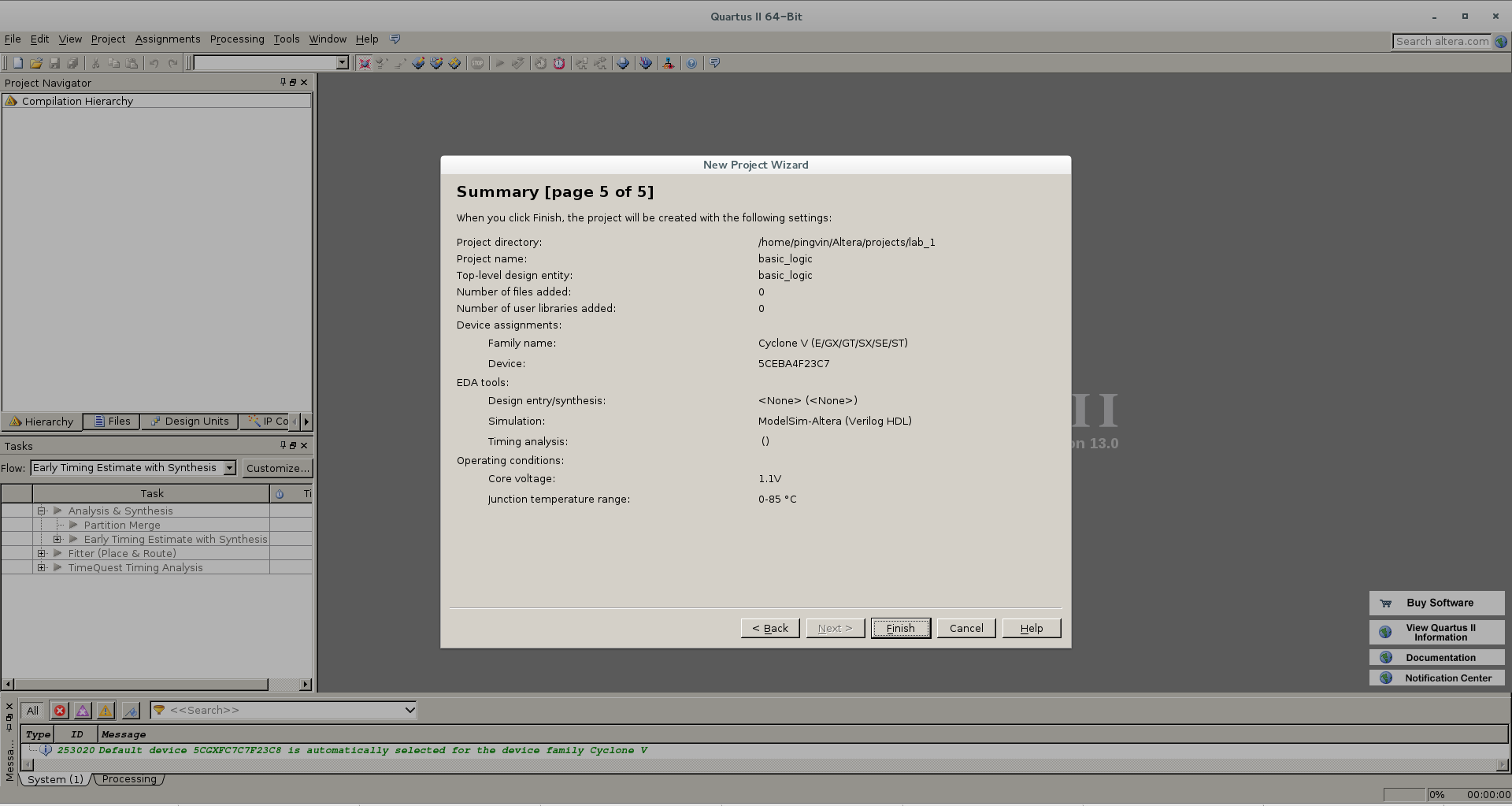

Теперь настало время важных настроек. На этом шаге нам надо выбрать кристалл, под который пишется проект. В принципе если вы ошибетесь или захотите перекомпиллировать проект под другое устройство — это можно будет исправить позже.

Здесь нам предлагают выбрать дополнительные инструменты. Мы пока оставляем все как есть и жмем Next.

Ну вот, мы выполнили первоначальные настройки и создали проект. Жмем Finish.

Теперь нам нужно создать файл, описывающий логику проекта. Заходим в меню File/New, появляется диалог в котором требуется выбрать тип файла. В принципе логику можно нарисовать в специальном графическом редакторе, но сейчас мы выбираем Verilog HDL File:

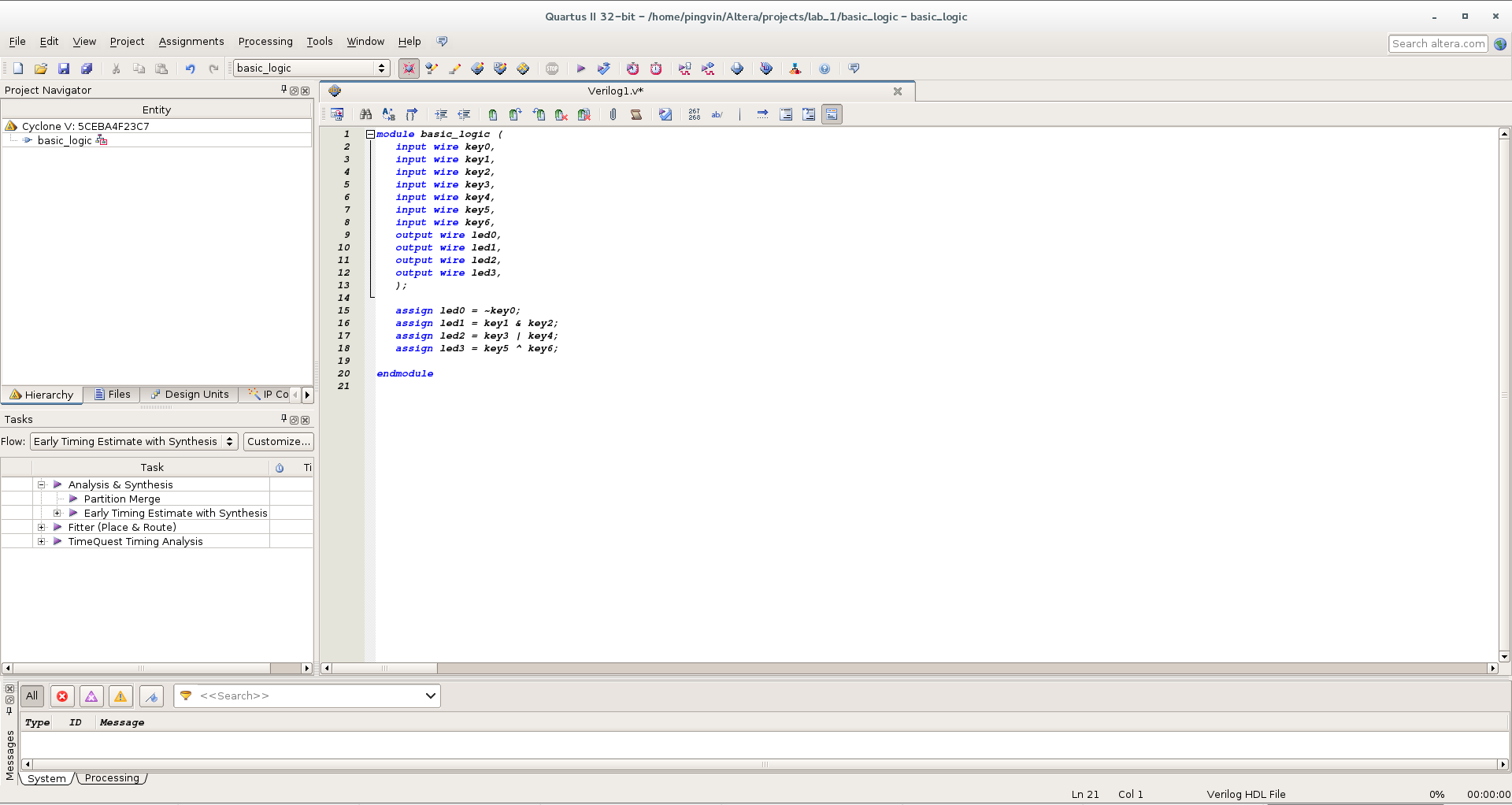

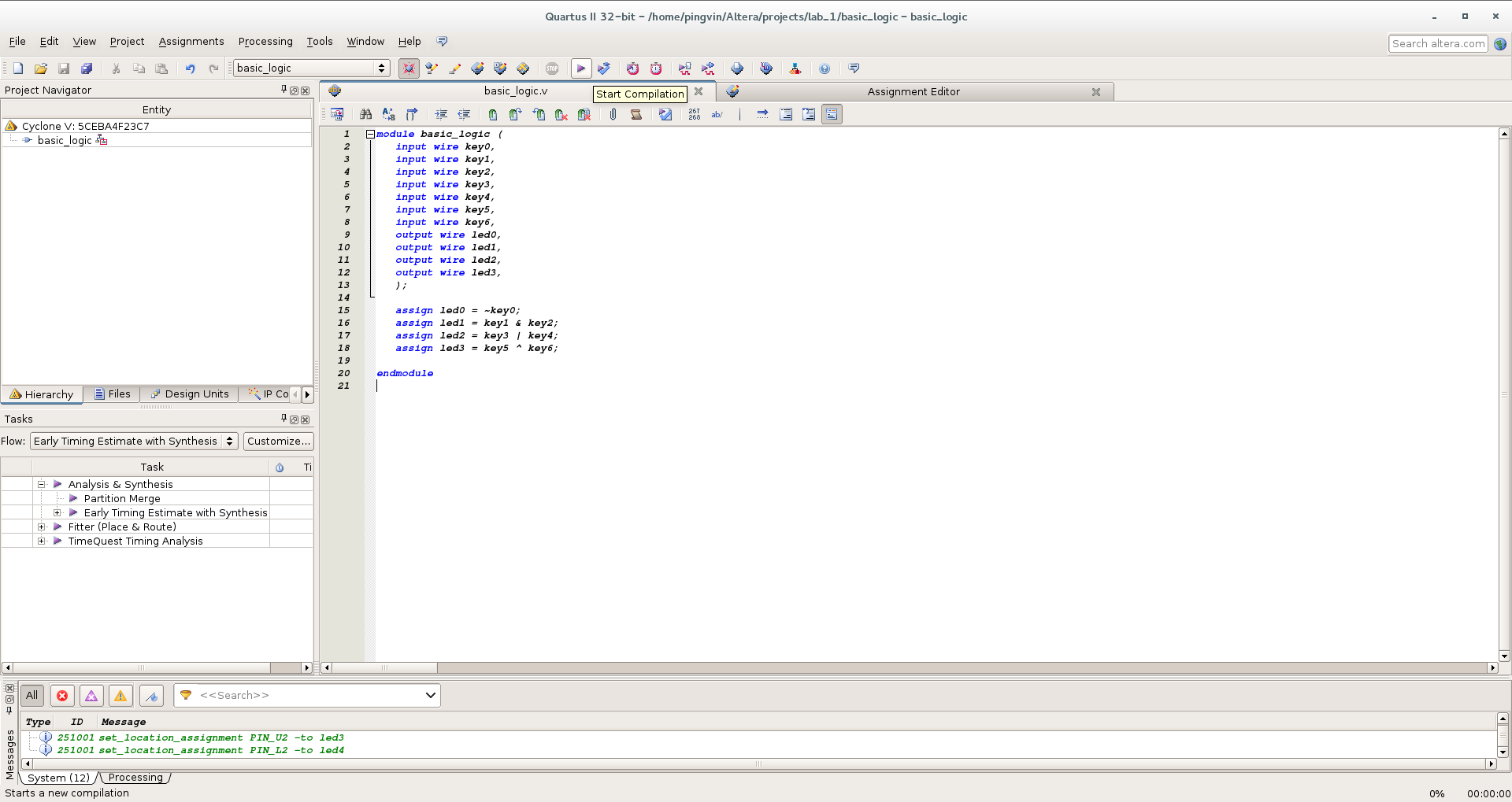

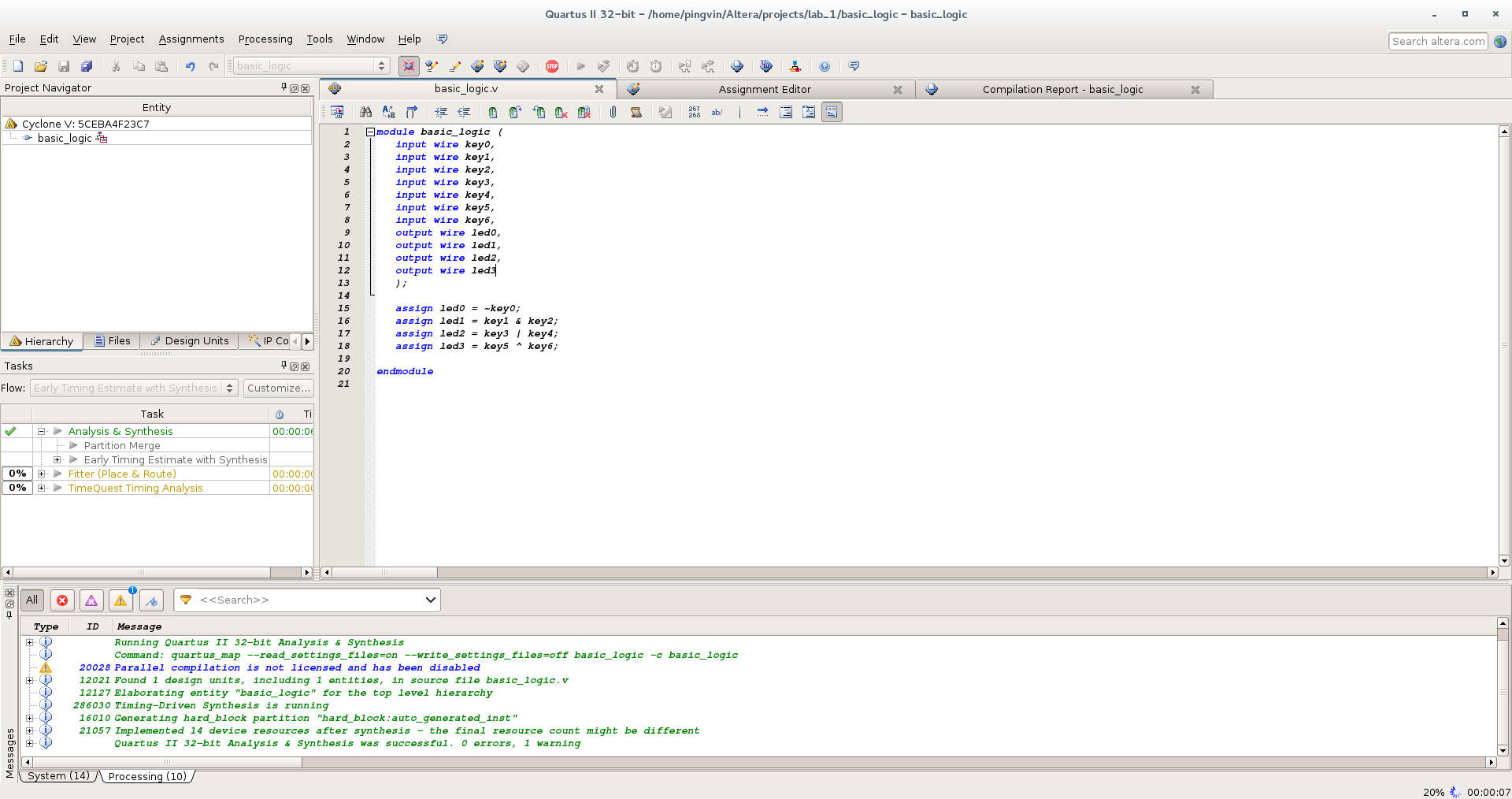

Файл создан, пишем текст нашей программы, описывающей элементы NO, AND, OR, XOR. В качестве входов используем, имеющиеся на плате переключатели (key*), а состояние выхода индицируем светодиодами (led*). Небольшая ремарка: производитель платы предлагает создать конфигурационный файл для входов-выходов в специальной программе, работающей только под Windows. Если пойти этим путем, то надо следить чтобы имена «проводов» и «регистров» в программе совпадали с таковыми в конфигурационном файле. Но мы сейчас будем делать все вручную, поэтому вольны выбрать любые имена.

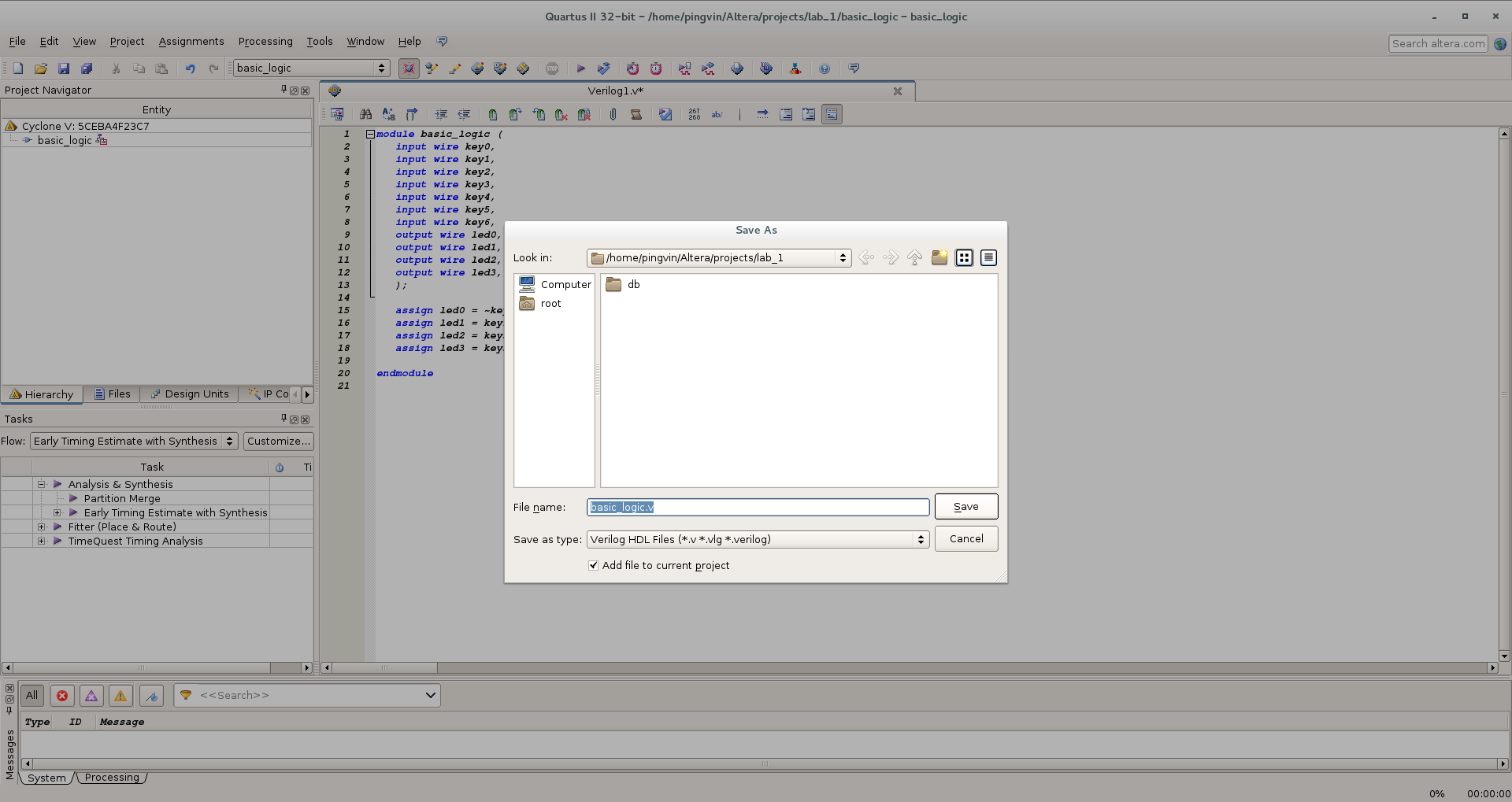

Теперь сохраняем файл. Важный момент — для корректной работы необходимо, чтобы имя файла совпадало с именем модуля, описываемого в программе (В нашем примере basic_logic).

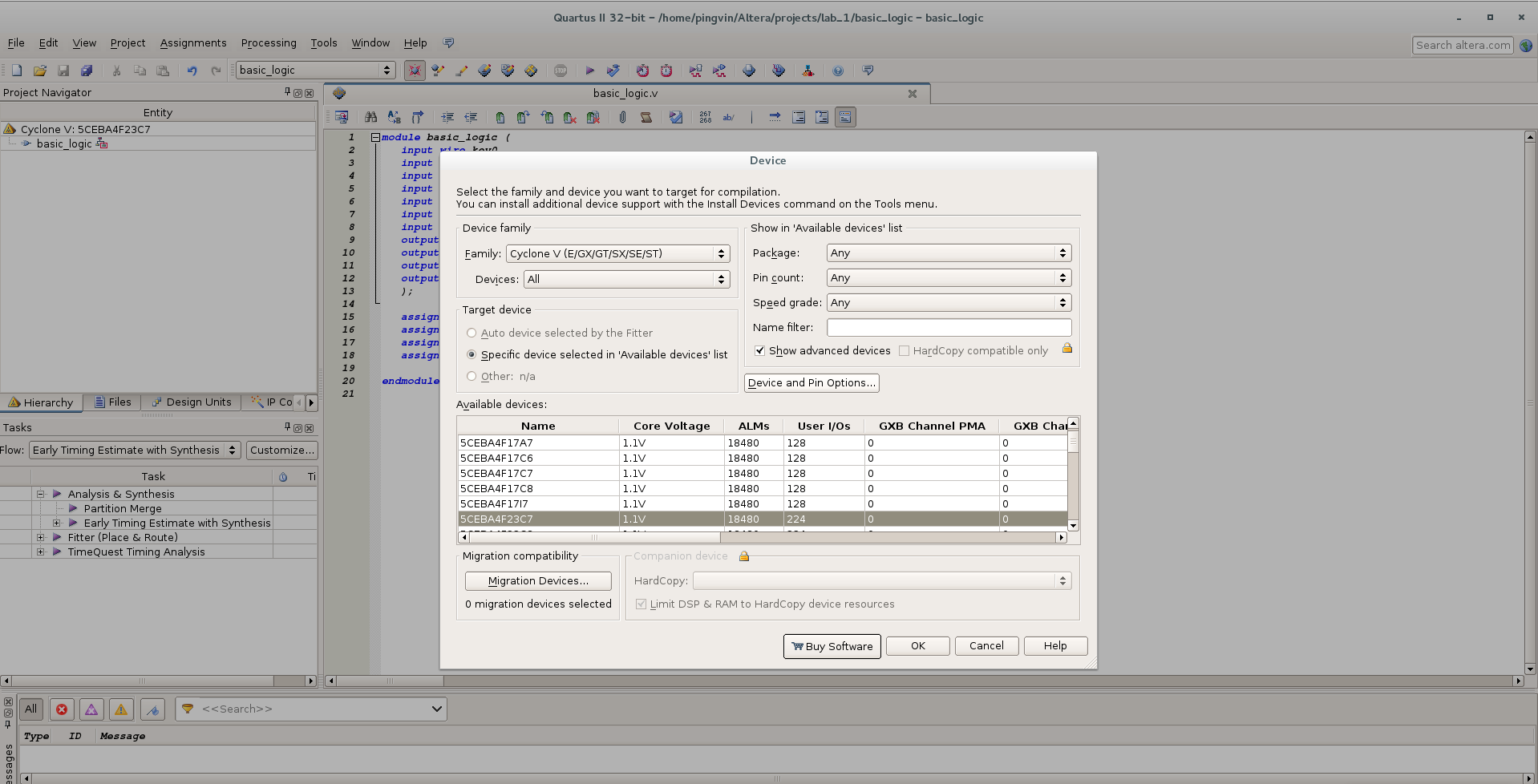

Теперь необходимо сделать ряд настроек для успешной компиляции проекта. Во-первых укажем, какой модуль у нас главный явным образом. Конкретно в этом проекте это не актуально, но для сложных проектов с множеством модулей этот шаг обязателен. Заходим в меню Project/Set As Top Level Entity. Готово. Далее надо сделать ряд настроек для конкретного кристалла. Выберем пункт меню Assignments/Device. Открывается диалог, в котором мы имеем возможность изменить тип кристалла (или проверить, что ранее мы его указали верно):

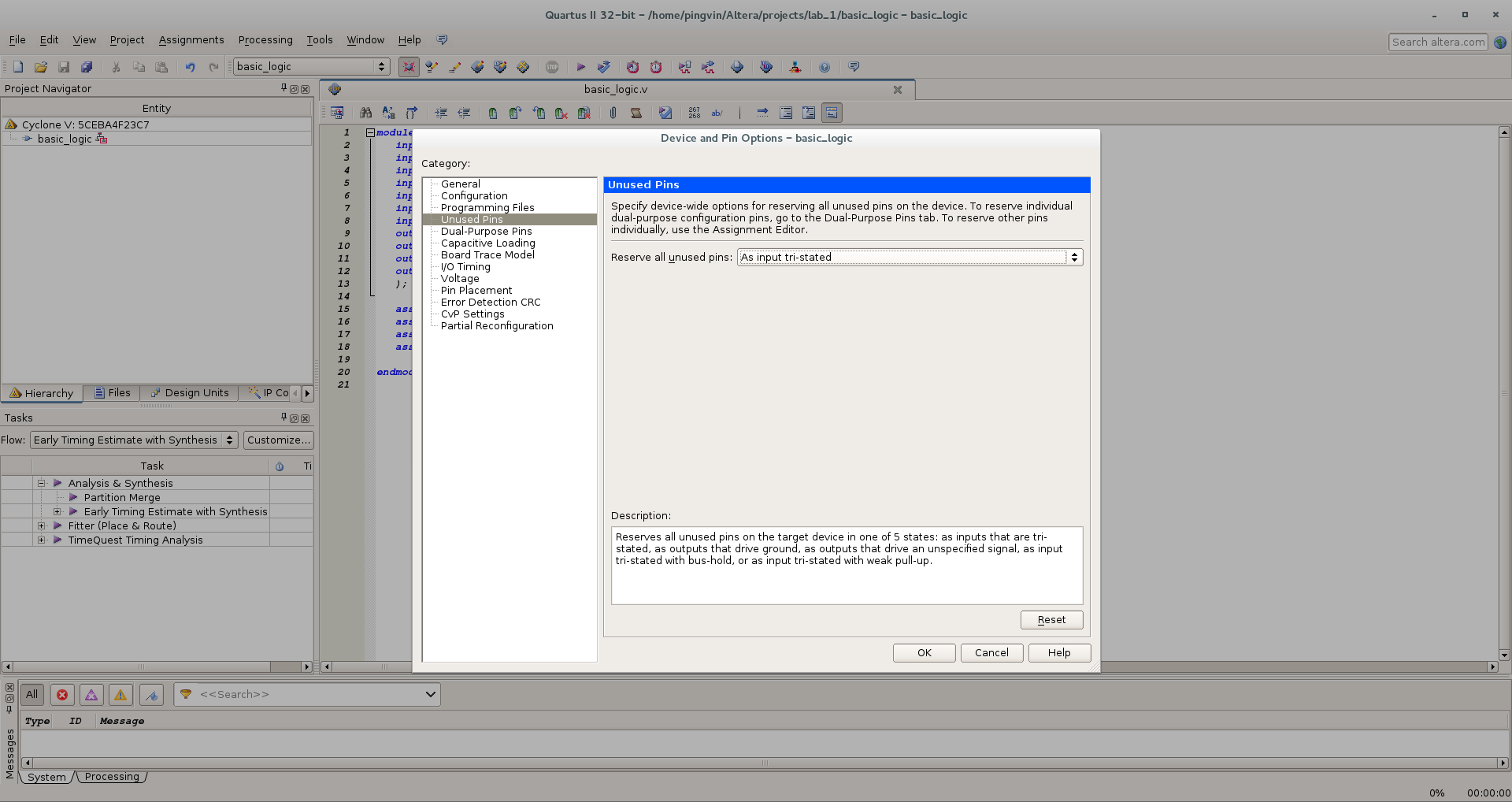

Теперь жмем кнопку Device and Pin Option и в открывшемся диалоге в первую очередь зададим состояние для неиспользуемых выводов. По умолчанию все неиспользуемые контакты микросхемы подключаются к нулю по питанию. Но мы не знаем, как эти выводы разведены физически на плате и такая конфигурация может привести к короткому замыканию и выходу из строя чипа. Поэтому безопасней неиспользуемые выводы сделать входами с высоким сопротивлением — As input tri-stated

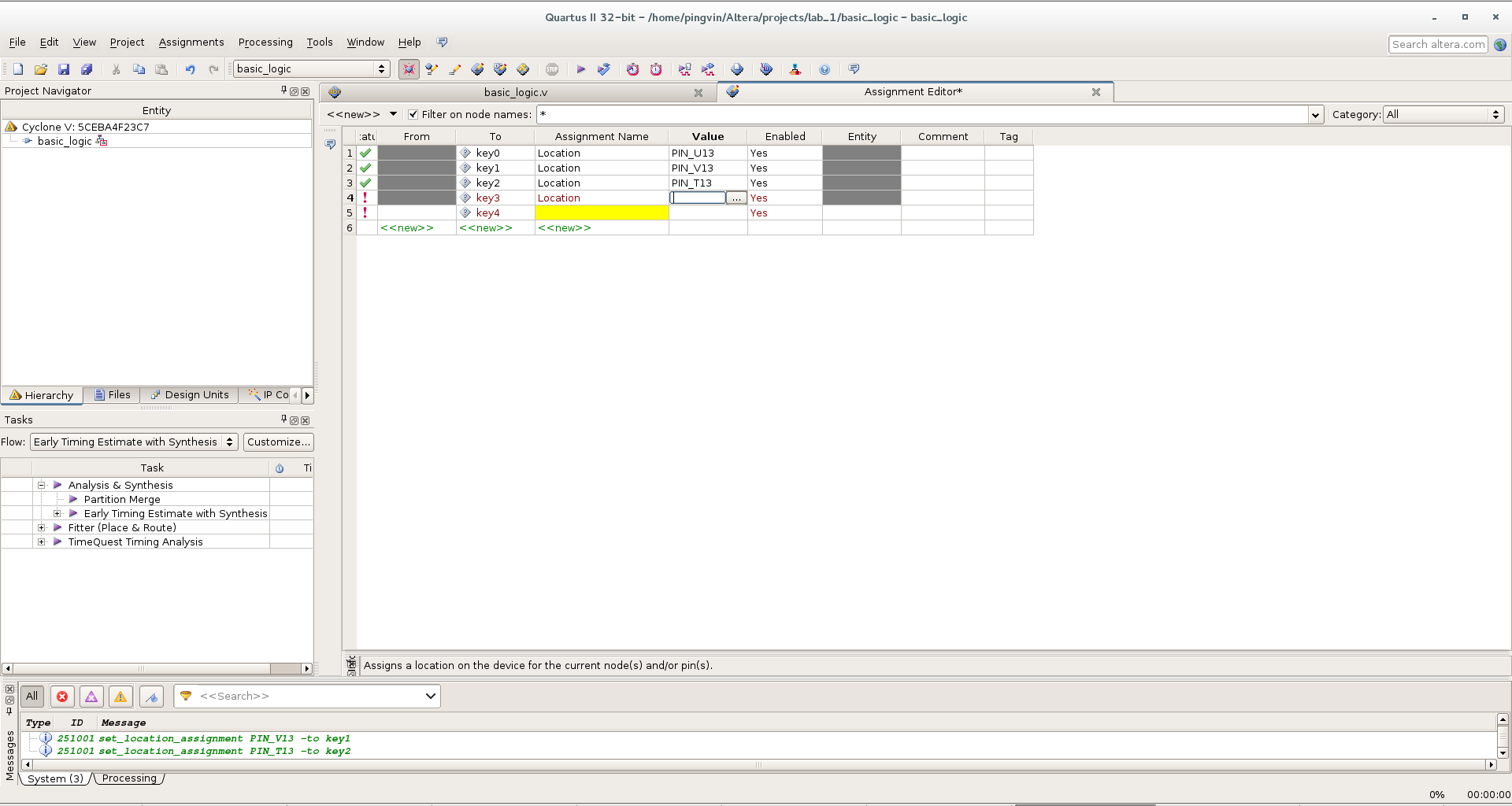

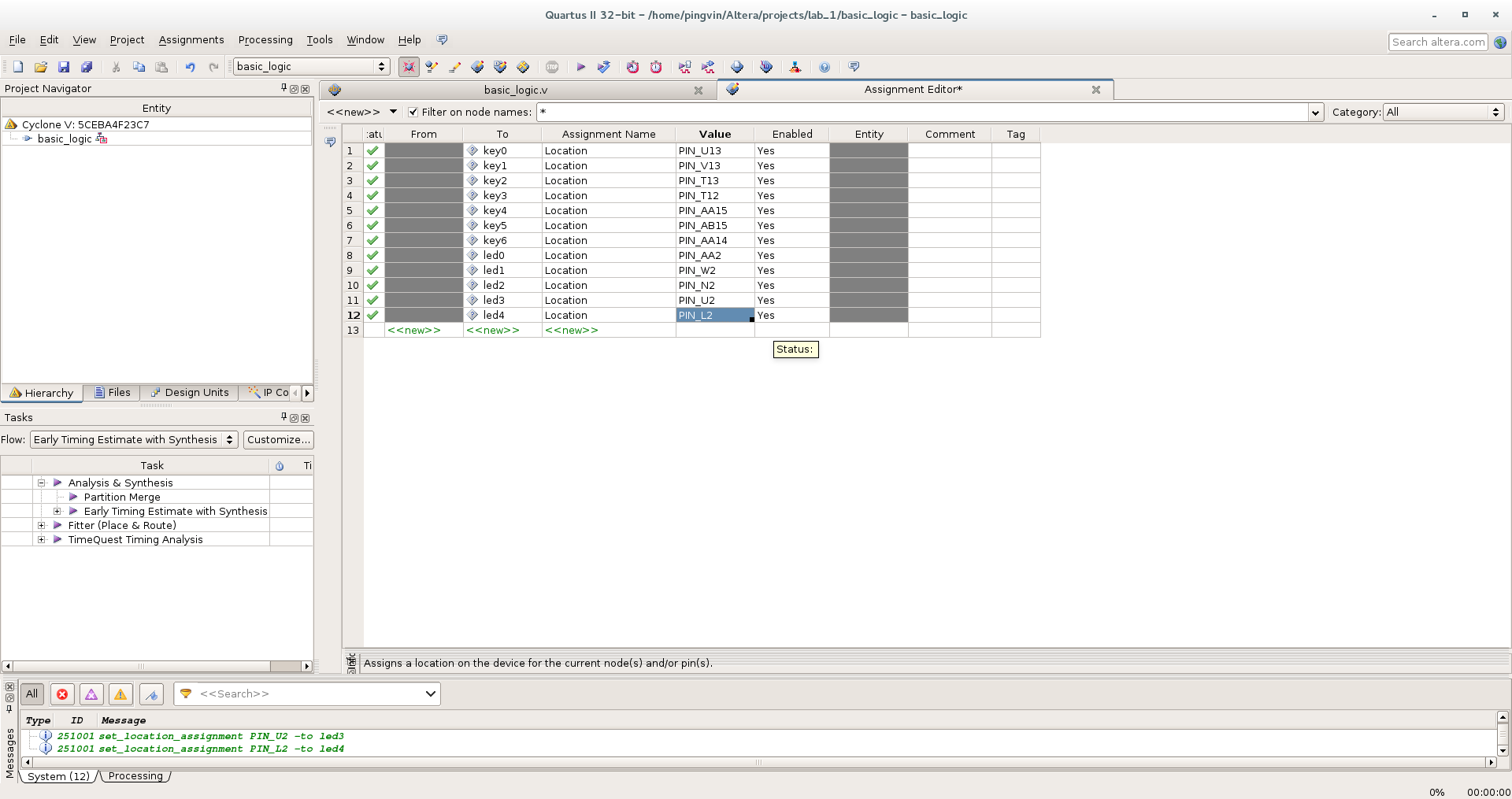

Следующий необходимый шаг — указать, какие физические ножки микросхемы соответствуют входам и выходам описанного нами модуля. Для этого идем в меню Assignments/Assignment Editor. В открывшемся окне делаем нужные нам назначения согласно схеме нашей платы. В колонке To вписываем имя входа или выхода. В колонке Assignment Name выбираем из списка нужную нам настройку Location. В колонке Value вписываем название контакта микросхемы:

Закономерный вопрос: откуда берется название контактов? Обычно в даташите на плату или конкретную микросхему есть табличка PIN OUT. Так же, как я ранее писал, с платой может идти специальная программа, создающая конфигурационный файл. А сейчас вы можете воспользоваться этими данными:

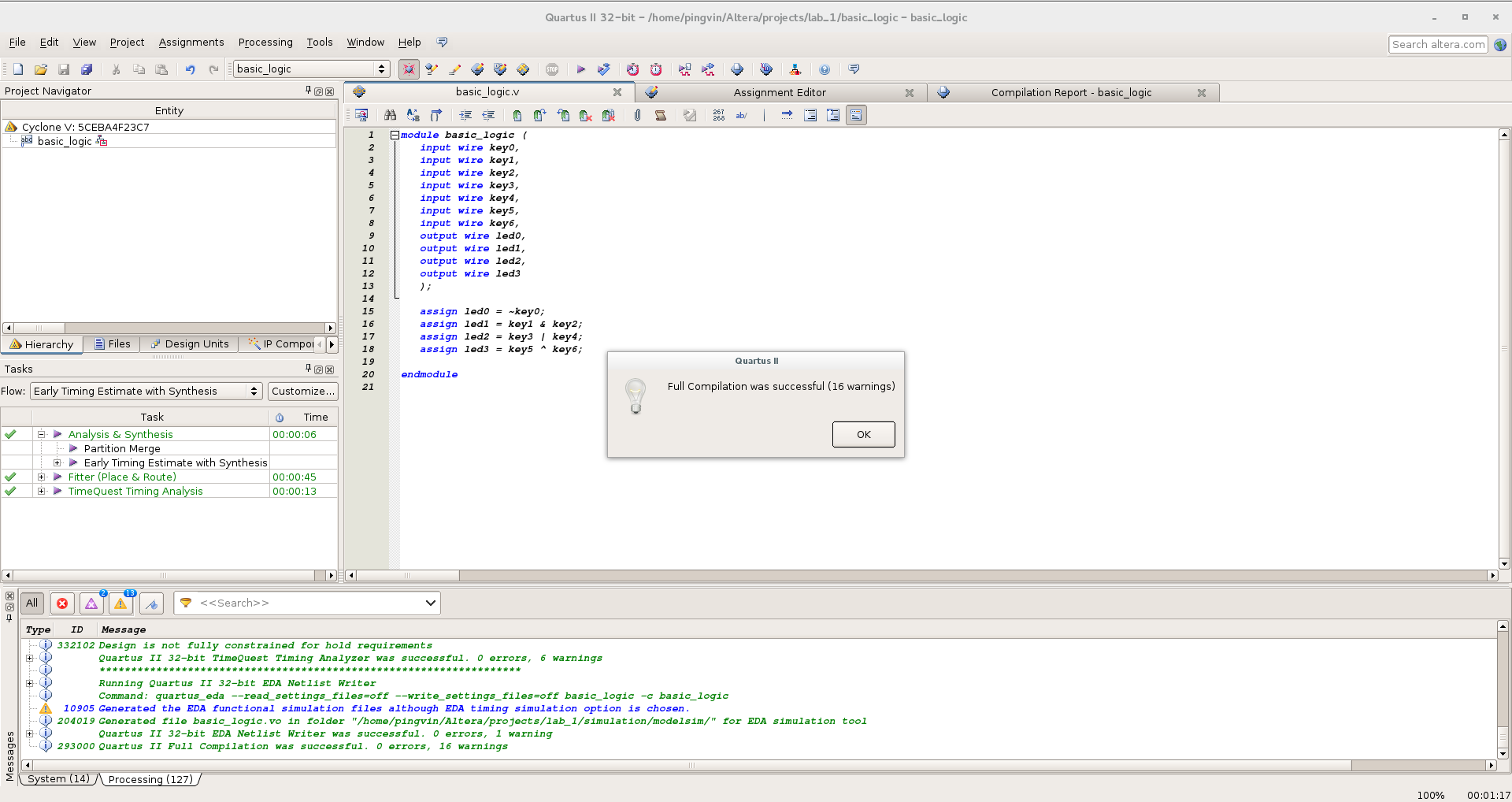

Наконец-то можно нажать кнопочку Start Compilation!

Получаем 16 warnings. Ничего серьезного.

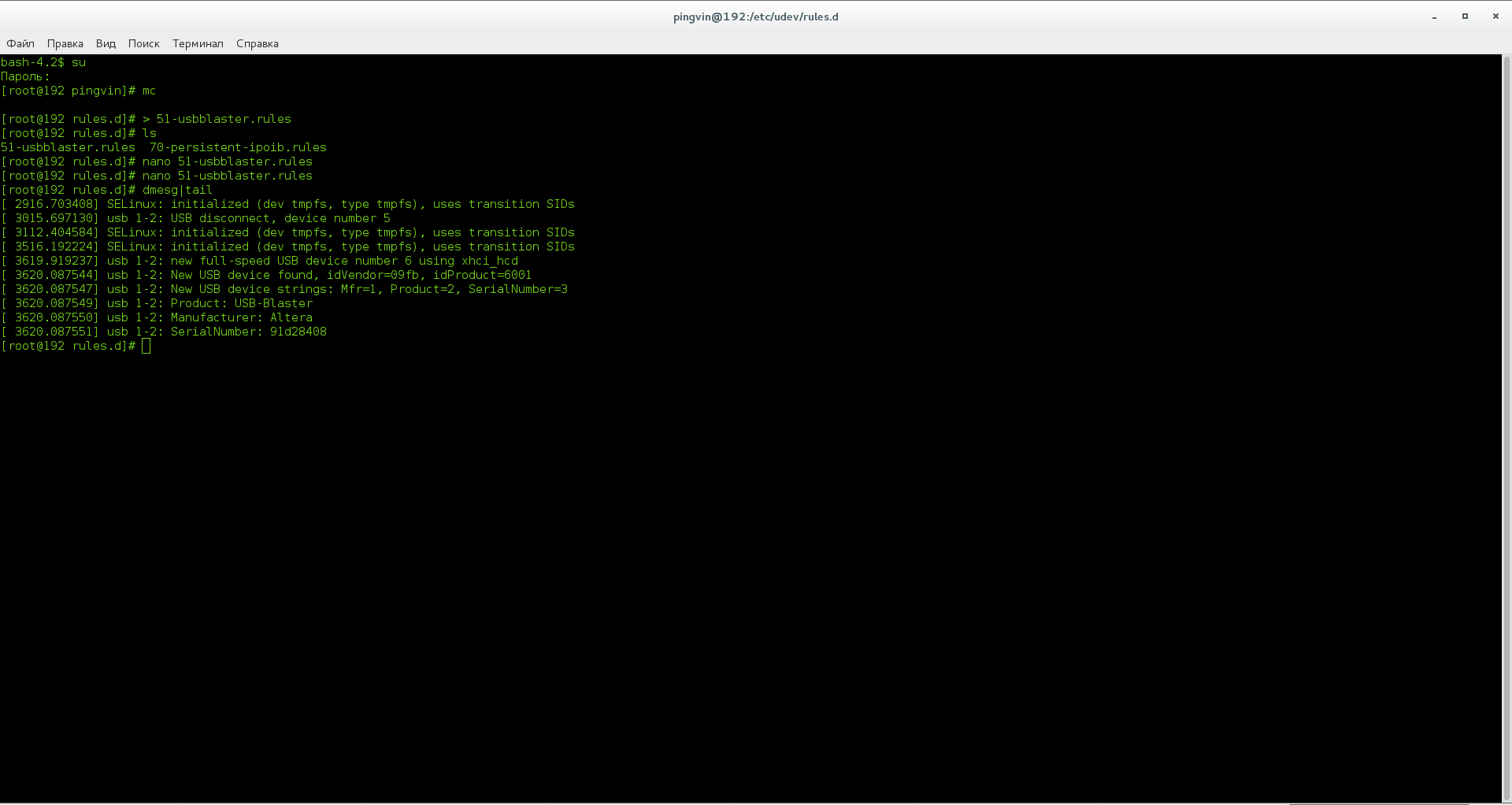

Теперь подключаем плату и запускаем программу программатора: Tools/Programmer. Линукс автоматически подхватывает USB-Blaster, но прошивка не работает… Что же, открываем любимую консоль, вооружаемся бубном и погружаемся в документацию к Quartus…

Для начала убеждаемся, что система видит программатор:

Переходим в папку /etc/profile.d/ , где создаем файл custom.sh

А затем в папке /etc/udev/rules.d/ файл с названием 51-usbblaster.rules И наполняем его

смыслом:

Теперь все работает и прошивка прекрасно вгружается в чип:

Любуемся результатом, играемся переключателями, мигая светодиодиками:

Using Altera’s Intel’s USB-Blaster on Debian Linux

I’ve tested this on a Terasic DE4 board, but in theory it should work with any board which uses a USB-Blaster interface to the JTAG chain for programming Altera FPGA devices, such as the DE2 commonly used for education.

Additionally, Carl Wernhoff also solved the same problem: Altera USB-Blaster with Ubuntu 14.04

The usbfs instructions are obsolete, as usbfs has ceased to exist in the Linux kernel as of 3.5. I’m keeping them here for historical interest, and also because the debugging guide at the end is still relevant.

Create a new udev rule: /etc/udev/rules.d/51-altera-usb-blaster.rules # USB-Blaster SUBSYSTEM=="usb", ATTR=="09fb", ATTR=="6001", MODE="0666" SUBSYSTEM=="usb", ATTR=="09fb", ATTR=="6002", MODE="0666" SUBSYSTEM=="usb", ATTR=="09fb", ATTR=="6003", MODE="0666" # USB-Blaster II SUBSYSTEM=="usb", ATTR=="09fb", ATTR=="6010", MODE="0666" SUBSYSTEM=="usb", ATTR=="09fb", ATTR=="6810", MODE="0666" Then, reload that file using udevadm: # udevadm control --reload

The rest of the instructions remain essentially the same: jtagd must run as root to ensure sufficient permissions.

Allowing non-root access to the USB-Blaster device

To do this, create a file called /etc/udev/rules.d/altera-usb-blaster.rules containing a single line:

This grants rw-rw-rw- permision to the device. A more proper configuration involves creating a group for the device, say usbblaster , placing your user(s) in that group, and defining the device permisions like so:

Note that this is not perfect: multiple USB device entries are created for the USB-Blaster, and not all will have the new permissions, which is why jtagd must run as root. (see below)

Mounting the usbfs filesystem

Add the following entry to /etc/fstab and mount it:

none /proc/bus/usb usbfs defaults 0 0

You’ll know its good if /proc/bus/usb/devices appears and spits out a bunch of textual device info when printed.

Note that Ubuntu no longer ships with usbfs enabled. This makes for more complicated workarounds, which you will find online.

Configuring jtagd

Quartus uses a daemon, jtagd , as intermediate bewteen the programming software and the device. This seems needlessly complicated, but does enable remote host programming apparently. The key points to configuring it correctly are: it must be able to access a list of FPGA descriptions, and run as root.

Copy the descriptions from your Quartus installation to the configuration directory of jtagd :

mkdir /etc/jtagd

cp /linux/quartus/linux/pgm_parts.txt /etc/jtagd/jtagd.pgm_parts (Note the change of name!)

Have jtagd start at boot by either placing it in the rc.d system, or simply place the followwing line in /etc/rc.local :

Although it might get created automatically, you can create an empty file named .jtagd.conf in your home directory. I hear it’s possible to edit it to allow external hosts to connect and program/debug. This is only necessary if you want to use that feature.

Testing your setup

As a final test, plug in your device, run dmesg to see if the USB-Blaster device is found, then run (as your usual user) jtagconfig . You should see output similar to this:

1) USB-Blaster [USB 1-1.1] 020B30DD EP2C15/20

If USB device permissions are insufficient (they shouldn’t, given the rule added in /etc/udev/rules.d/altera-usb-blaster.rules ), you will instead get:

No JTAG hardware available

If USB permissions are OK, but jtagd is not running as root, you will see:

1) USB_Blaster [USB 4-1.2] Unable to lock chain (Insufficient port permissions)

Finally, if permissions are OK and jtagd is running as root, but it cannot access the FPGA device descriptions, you will see:

1) USB-Blaster [USB 4-1.2] 024030DD

Programming your FPGA device

You should now be able to use the Programmer in Quartus to load a bitstream onto your target FPGA. Alternately, you can use the following shell script to do it at the command line:

#!/bin/bash quartus_pgm -z -m JTAG -o "p;$1"